# **Understanding Multi-Stream**

#### **VESA DisplayPort Workshop, Taipei May 2013**

Bob Crepps Lexus Lee

Technical Marketing Engineer, VTM Inc. Compliance Program Manager, Allion Labs

Compliance Program Manager, VESA Sales Manager, Allion Labs

#### **Multi-Stream Basics**

- MST Extension

- MTP (Multi-Stream Transport Packet)

- VC (Virtual Channel) Payload

- Video Stream Symbol Mapping within VCP

- Addition/Deletion of Streams

- MST Topology Management

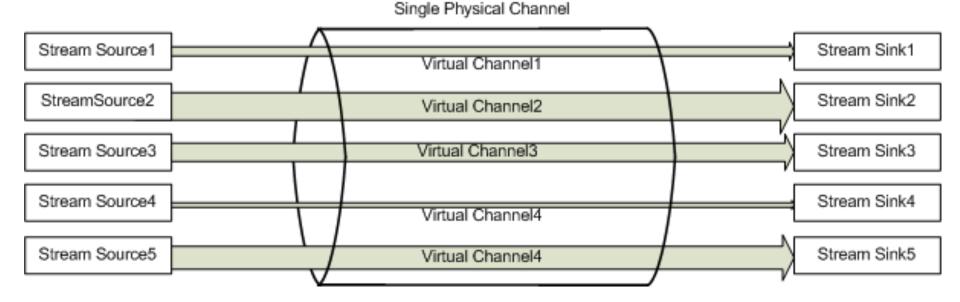

## MST (Multi-Stream Transport) Extension

De-coupling of Virtual Channels between stream sources and stream sinks from physical channels

**NOTE:** Widths of the arrows imply stream bandwidths

## **MST Extension** (continued)

- Micro-Packet-based, time-division multiplexing to enable transport of multiple AV streams over a single physical connection

- In theory, up to 63 AV streams transportable concurrently

- Not "one stream per lane"

- No synchronicity assumed among streams transported over a single physical channel

- E.g., Streams may have different frame rates (24Hz / 25Hz /50Hz/ 59.94Hz /60Hz / 72Hz /75Hz...)

- Addition/deletion of a stream without affecting the remaining streams

- Packetizing overhead as small as 1.6%

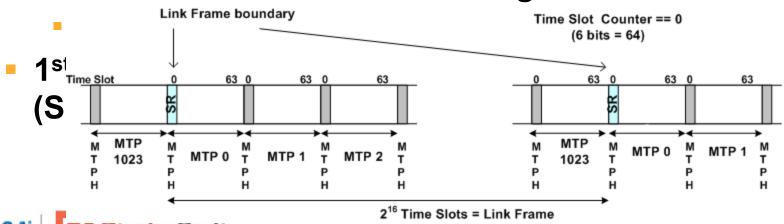

## MTP (Multi-Stream Transport Packet)

- The unit of Micro-Packet in MST Mode

- 64 time slots long

- 1st time slot of MTP used as MTP Header

- Remaining 63 time slots allocated to carry streams

- Carries 00's when unallocated for a stream transport

- 1024 MTP's constitute a "Link Frame"

- 1 Link frame = 2<sup>16</sup> time slots long

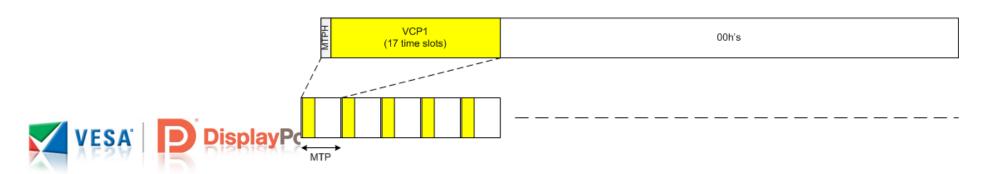

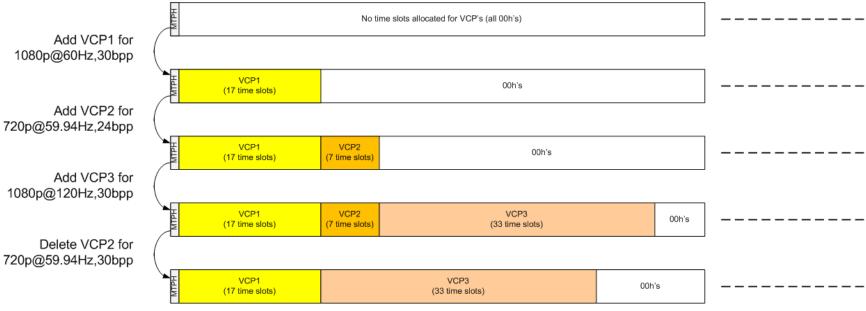

## VC (Virtual Channel) Payload

- VC Payload = Time slots within MTP (excluding MTP Header) allocated for transporting a stream

- One AV stream per VC Payload

- Example: 1080p60Hz, 30bpp over 4-lane, 5.4Gbps/lane Main Link

- Pixel bandwidth = 148.5Mpixels/sec \* (30/8) bytes/pixel = 556.875Mbytes/sec

- 1 time slot per MTP = 540Mbytes/sec/lane \* 4 lanes / 64 time slots per MTP

- = 33.75Mbytes/sec/time slot

- VC Payload time slot count for this stream over this Main Link (VCP1)

- = CEIL (556.875 / 33.75) = 17 time slots

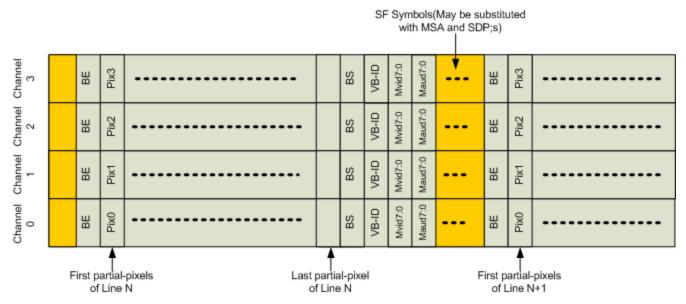

## Video Stream Symbol Mapping within VCP

- Active video pixel data framed with BE and BS Control Symbols

- When no pixel to transport (e.g., video blanking period), insert SF (Stream Fill) control symbols

- MSA (Main Stream Attributes) Packet to replace SF symbols once per vertical blanking interval to describe video stream attributes

**NOTE:** Stream symbols carried in a VCP form the above when concatenated across MTP's

### Addition/Deletion of Streams

- One stream at a time

- Time slot allocation change agreed on between TX and RX via sideband communication

- Addition/deletion of a VC Payload over Main Link synchronized between TX and RX by inserting ACT (Allocation Change Trigger) symbol in four consecutive MTP Headers preceding the change

#### **GUID**

### **Global Unique Identifier**

- Topology Management Layer identifies each MST device in a branching unit

- MST device may perform more than one function i.e. USB hub.

- GUID identifies the physical unit that contains multiple functions

- Source assigns 16-byte GUID unless the device already has one

## **DP Audio Transport**

- Available bandwidth supports 4Kx2K 60Hz progressive, YCbCr444 30bits per pixel and 2 streams of 192kHz, 22.2ch audio

- Audio transport without video supported

- Multi-Stream allows routing of multiple audio streams to multiple audio rendering devices

- Audio inter-channel synchronization across multiple audio rendering devices supported

- Aligns real-time clock of each device in 100-ns precision via GTC (Global Time Code)

- Audio stream source device to specify the presentation time of an audio frame in the audio stream packet

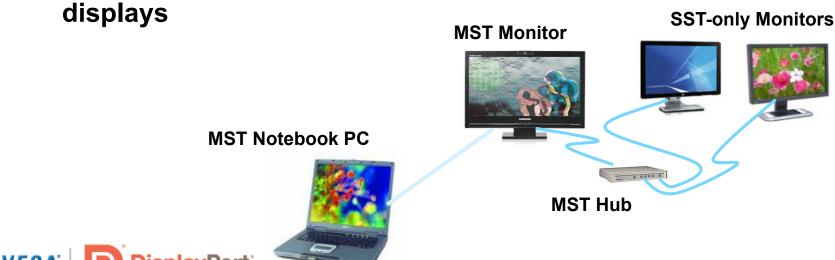

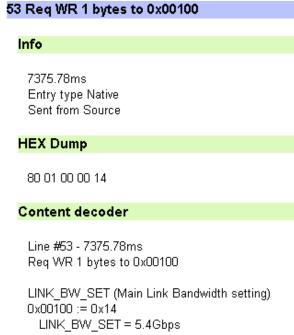

## **MST Topology Management**

- Node addressing through discovery procedure

- Topology Manager (typically a DP Source device) discovers the path to the other DP device

- Plugging/unplugging of a device handled without resetting the address set of the entire link

- Supports topology containing multiple DP Source and Sink devices

Initial main focus: a single DP Source device driving multiple displays

SST-only Monitors

#### **Multistream Reference**

#### Multi-Stream Use Case Example 1.0

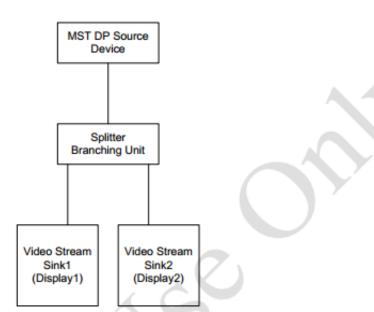

#### 1 Example MST Topology without Audio Stream Sink

This document covers how an MST DP Source device and a device containing MST Branching Unit are to interact to perform typical topology and payload bandwidth management functions in the following logical topology.

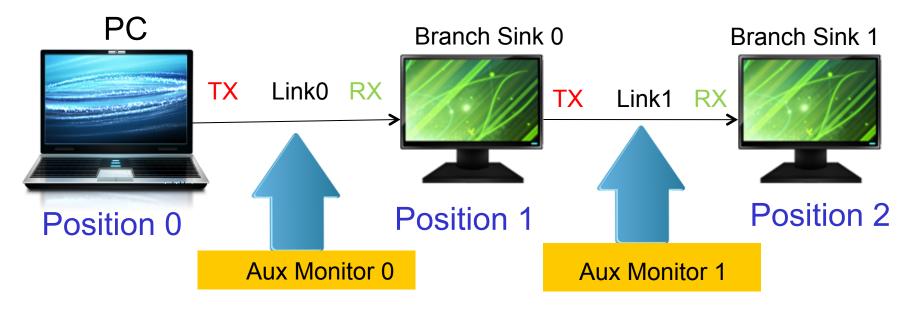

Figure 1-1: Logical Topology Covered in this Document

# **Understanding Multi-Stream**

#### **VESA DisplayPort Workshop, Taipei May 2013**

**Bob Crepps**

**Technical Marketing Engineer, VTM Inc.**

**Compliance Program Manager, VESA**

**Lexus Lee**

**Compliance Program Manager, Allion**

Labs

**Sales Manager**, Allion Labs

- MST Compliance Test Introduction

- Protocol Test

- Source

- Branch Sink or Hub

- Multi-Stream Sink

- Interoperability Test

- Source

- Branch Sink or Hub

- Multi-Stream Sink

- 5 Configurations for Protocol Test

- Configuration A

- Configuration B

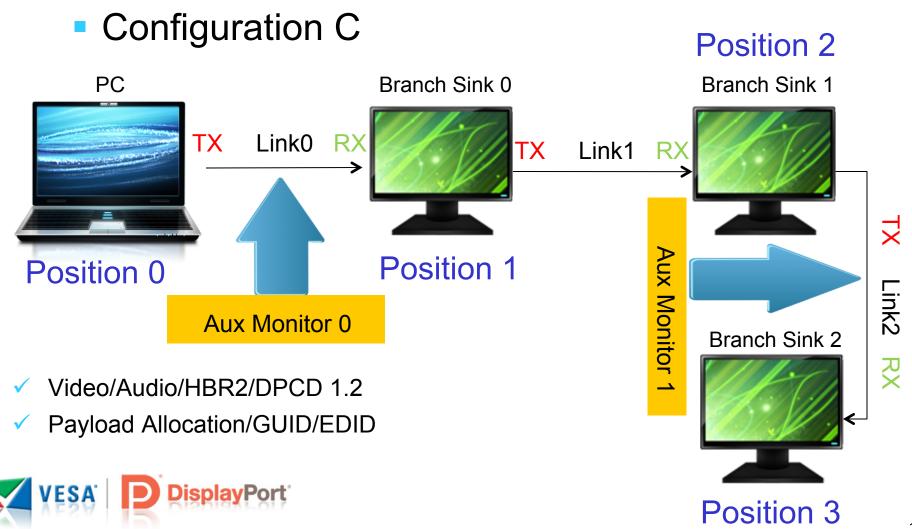

- Configuration C

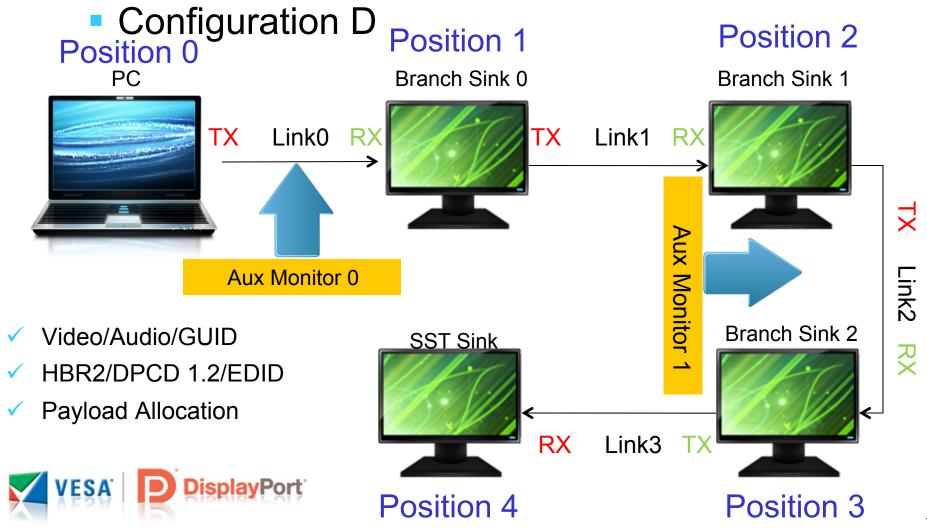

- Configuration D

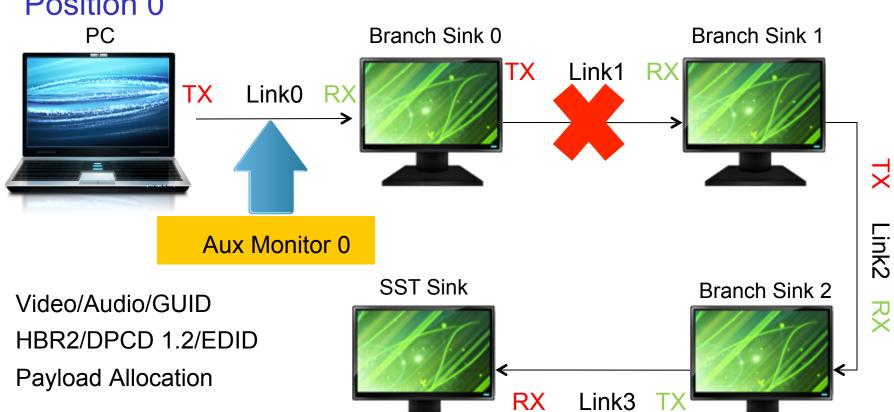

- Configuration E

- Protocol Test

- Configuration A

- ✓ Video

- ✓ Audio

- ✓ HBR2

- ✓ DPCD 1.2

- PayloadAllocation

- **✓** GUID

- ✓ EDID

- Protocol Test

- Configuration B

- ✓ Video/Audio/HBR2/DPCD 1.2

- ✓ Payload Allocation/GUID/EDID

Protocol Test

#### Protocol Test

### Protocol Test

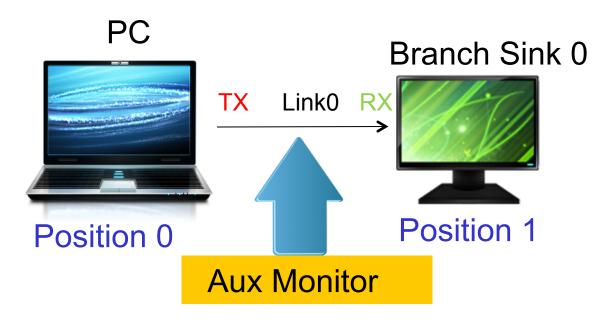

# Configuration EPosition 0

## **Interop Test Matrix**

#### **Branch Sink**

| Pos 0 | Source |

|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| Pos 1 | DUT    | DUT    | DUT    | DUT    | DUT    | BS0    |

| Pos 2 |        | BS0    | BS0    | BS0    | BS0    | DUT    | DUT    | DUT    | DUT    | BS1    | BS1    | BS1    | BS1    |

| Pos 3 |        |        | BS1    | BS1    | BS1    |        | BS1    | BS1    | BS1    | DUT    | DUT    | BS2    | BS2    |

| Pos 4 |        |        |        | BS2    | BS2    |        |        | BS2    | BS2    | BS2    | BS2    | DUT    | DUT    |

| Pos 5 |        |        |        |        | SST    |        |        |        | SST    |        | SST    |        | SST    |

Reference: DP 1.2a Standard

Table 2-75: Address Mapping for DPCD

| DisplayPort<br>Address | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Read/Write<br>over AUX CH |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

|                        | Receiver Capability Field                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                           |

| 00000h                 | DPCD_REV: DPCD revision number  Bits 3:0 = Minor revision number  Bits 7:4 = Major revision number  10h for DPCD Rev.1.0  11h for DPCD Rev.1.1  12h for DPCD Rev 1.2  A DP device with uPacket RX with a DPCD Revision number of 1.2 and above must support GUID at DPCD Addresses 00030h ~ 0003Fh. Furthermore, a DP Sink device with DPCD Rev.1.2 with a stereo display capability support (as declared in EDID and Display ID) must support the handling of 3D Stereo inband signaling using Video_Stream_Configuration (VSC) Packet.  Note: The DPCD revision number does not necessarily match the DisplayPort version number. | Read Only                 |

| 00001h                 | MAX LINK RATE: Maximum link rate of Main Link lanes = Value x 0.27Ghns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Read Only                 |

Reference: DP 1.2a Standard

| Definition                                                                                                                                                                                                                            | Read/Write<br>over AUX CH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Link Configuration Field                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

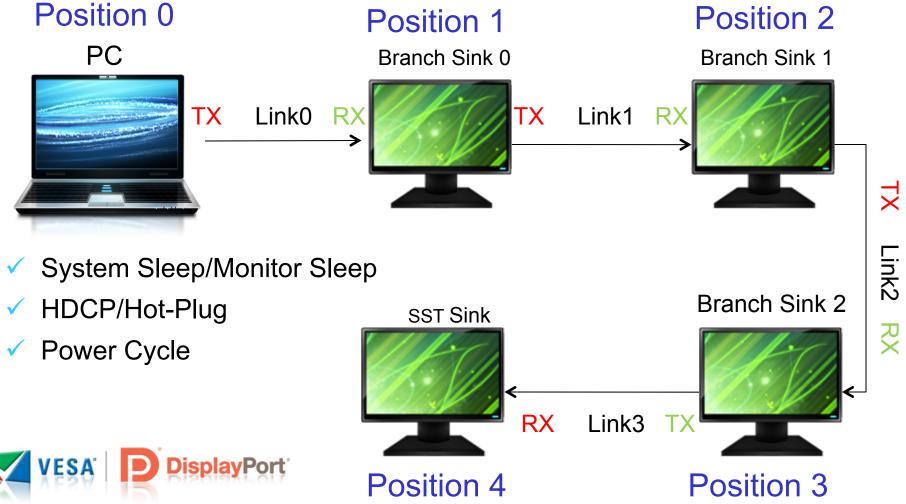

| LINK_BW_SET: Main Link Bandwidth Setting=Value x 0.27Gbps per lane Bits 7:0 = LINK_BW_SET For DisplayPort Version 1, Revision 1a, only three values are supported. All other values are RESERVED.                                     | Write/Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 06h = 1.62Gbps per lane<br>0Ah = 2.7Gbps per lane<br>14h = 5.4Gbps per lane                                                                                                                                                           | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| The Source may choose any of the three link bandwidths as long as it does not exceed the capability of DisplayPort receiver as indicated in the receiver capability field.                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| LANE_COUNT_SET: Main Link Lane Count = Value  Bits 4:0 = LANE_COUNT_SET  For DisplayPort Version 1, Revision 1a, only the following three values are supported. All other values are RESERVED.  1h = 1-lane 2h = 2-lanes 4h = 4-lanes | Write/Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|                                                                                                                                                                                                                                       | Link Configuration Field  LINK_BW_SET: Main Link Bandwidth Setting=Value x 0.27Gbps per lane Bits 7:0 = LINK_BW_SET For DisplayPort Version 1, Revision 1a, only three values are supported. All other values are RESERVED.  06h = 1.62Gbps per lane 0Ah = 2.7Gbps per lane 14h = 5.4Gbps per lane The Source may choose any of the three link bandwidths as long as it does not exceed the capability of DisplayPort receiver as indicated in the receiver capability field.  LANE_COUNT_SET: Main Link Lane Count = Value Bits 4:0 = LANE_COUNT_SET For DisplayPort Version 1, Revision 1a, only the following three values are supported. All other values are RESERVED.  1h = 1-lane 2h = 2-lanes |  |  |  |  |  |  |

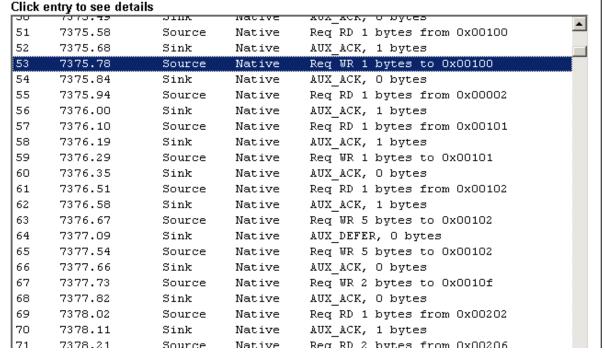

#### Check Link Training= HBR2

#### Link may not train to HBR2 if bandwidth need is lower

#### Check for DPCD Revision= 1.2

#### Unigraf DisplayPort AUX Channel monitor report TRANSACTION DETAILS AUX CHANNEL TRANSACTIONS AND EVENTS Click entry to see details 4 AUX ACK, 1 bytes 0.00 DPA-400 INFO Start: HPD=Low INO=High IN1=High IN2=Hi( 6867.65 Unknown Changed: HPD=High Event Info 7368.77 Source Native Req RD 1 bytes from 0x00000 7368.83 Native AUX ACK, 1 bytes Sink 7368.83ms 7368.96 Req RD 5 bytes from 0x68000 Source Native Entry type Native 7369.02 Sink Native AUX ACK, 5 bytes Sent from Sink 7369.15 Source Native Req RD 1 bytes from 0x68028 8 7369.25 Sink Native AUX ACK, 1 bytes **HEX Dump** 7369.34 Source Native Req RD 1 bytes from 0x68029 10 7369.41 Sink Native AUX ACK, 1 bytes 00 12 11 7369.66 Req RD 16 bytes from 0x00000 Source Native 12 7369.76 Sink Native AUX ACK, 16 bytes Content decoder 13 7369.98 Source Native Req RD 3 bytes from 0x00020 7370.05 Sink Native AUX ACK, 3 bytes 15 7370.18 Source Native Req RD 1 bytes from 0x00330 Line #4 - 7368.83ms 7370.27 Sink Native AUX ACK, 1 bytes AUX ACK, 1 bytes 17 7370.37 Source Native Req RD 16 bytes from 0x00080 7370.43 Sink Native AUX ACK, 16 bytes DPCD\_REV [RO] (DPCD revision number) 19 7370.66 Source Native Req RD 1 bytes from 0x0050a 0x000000 := 0x1220 7370.75 Sink Native AUX ACK, 1 bytes DPCD V1.2 21 7370.85 Source Native Req RD 4 bytes from 0x02002

### Check for EDID from Sideband Messages

Show report information ...

| 200 | 0307.20 | ") TIIV   | Nacive   | AUA AUA, T NYCCO                     |

|-----|---------|-----------|----------|--------------------------------------|

| 237 | 8307.20 | Sink T.   |          | DOWN REP - Message Transaction fragm |

| 238 | 8307.36 | Source    | Native   | Req WR 1 bytes to 0x02003            |

| 239 | 8307.42 | Sink      | Native   | AUX ACK, O bytes                     |

| 240 | 8430.78 | Source    | Native   | Req RD 1 bytes from 0x00600          |

| 241 | 8430.85 | Sink      | Native   | AUX ACK, 1 bytes                     |

| 242 | 8440.03 | Source    | Native   | Req RD 1 bytes from 0x00600          |

| 243 | 8440.10 | Sink      | Native   | AUX_ACK, 1 bytes                     |

| 244 | 8472.93 | Unknown   | Event    | Changed: HPD=Low                     |

| 245 | 8473.86 | Unknown   | Event    | Changed:HPD=High                     |

| 246 | 8473.89 | Source    | Native   | Req RD 6 bytes from 0x00200          |

| 247 | 8473.98 | Sink      | Native   | AUX ACK, 6 bytes                     |

| 248 | 8474.21 | Source    | Native   | Req RD 4 bytes from 0x02002          |

| 249 | 8474.27 | Sink      | Native   | AUX ACK, 4 bytes                     |

| 250 | 8474.43 | Source    | Native   | Req RD 16 bytes from 0x01400         |

| 251 | 8474.53 | Sink      | Native   | AUX ACK, 16 bytes                    |

| 252 | 8474.72 | Source    | Native   | Req RD 16 bytes from 0x01410         |

| 253 | 8474.82 | Sink      | Native   | AUX ACK, 16 bytes                    |

| 254 | 8475.04 | Source    | Native   | Req RD 4 bytes from 0x01420          |

| 255 | 8475.10 | Sink      | Native   | AUX ACK, 4 bytes                     |

| 256 | 8475.10 | Sink T.   | Sb Reply | DOWN_REP - REPLY: REMOTE_I2C_READ    |

| 257 | 8475.23 | Source    | Native   | Req WR 1 bytes to 0x02003            |

| 258 | 8475.33 | Sink      | Native   | AUX_ACK, O bytes                     |

| 259 | 8475.42 | Source    | Native   | Req WR 12 bytes to 0x01000           |

| 260 | 8475.42 | Source T. | Sb Req.  | DOWN REQ - REQ: REMOTE 12C READ      |

| 261 | 8475.87 | Sink      | Native   | AUX DEFER, O bytes                   |

|     |         |           |          |                                      |

Unigraf Oy

Show printer friendly format ...

Line #256 - 8475.10ms DOWN REP - REPLY: REMOTE I2C READ

-- Sideband message header -Link\_Count\_Total = 1

Link\_Count\_Remaining = 0

Broadcast\_Message = 0

Path\_Message = 0

MSG\_Body\_Length = 33

Start\_Of\_MT = 0

End\_Of\_MT = 1

Message Sequence No = 0

-- Sideband message validity check --MSG\_Header\_CRC = 2 [Good] MSG\_Body\_CRC = 182 [Good] Header Reserved (Zero) fields = Good

-- Full Message Transaction body -0x00: 22 08 80 00 ff ff ff ff ff 00 10 ac 46 f0 4c

0x10: 30 38 43 31 16 01 04 b5 34 20 78 3a 1d f5 ae 4f

0x20: 35 b3 25 0d 50 54 a5 4b 00 81 80 a9 40 d1 00 71

0x30: 4f 01 01 01 01 01 01 01 01 28 3c 80 a0 70 b0 23

0x40: 40 30 20 36 00 06 44 21 00 00 1a 00 00 00 ff 00

0x50: 46 4e 38 46 59 32 43 37 43 38 30 4c 0a 00 00 00

0x60: fc 00 44 45 4c 4c 20 55 32 34 31 33 0a 20 20 00

0x70: 00 00 fd 00 38 4c 1e 51 11 00 0a 20 20 20 20

0x80:20:01:3b

#### **Check Allocate Payload**

| 918        | 10244.99             | Source    |                  |                                              |

|------------|----------------------|-----------|------------------|----------------------------------------------|

| 919        | 10244.99             |           |                  | DOWN_REQ - REQ: ALLOCATE_PAYLOAD             |

| 920        | 10245.44             | Sink      | Native           | AUX_DEFER, O bytes                           |

| 921        | 10245.92             | Source    | Native           |                                              |

| 922        | 10245.92             | Source T. | Sb Req.          | DOWN_REQ - REQ: ALLOCATE_PAYLOAD             |

| 923        | 10246.08             | Sink      | Native           | AUX_ACK, O bytes                             |

| 924        | 10246.18             | Source    | Native           | Req RD 4 bytes from 0x02002                  |

| 925        | 10246.24             | Sink      | Native           | AUX_ACK, 4 bytes                             |

| 926        | 10246.59             | Source    | Native           | Req RD 4 bytes from 0x02002                  |

| 927        | 10246.66             | Sink      | Native           | AUX_ACK, 4 bytes                             |

| 928        | 10247.01             | Unknown   | Event            | Changed: HPD=Low                             |

| 929        | 10247.58             | Source    | Native           | Req RD 4 bytes from 0x02002                  |

| 930        | 10247.68             | Sink      | Native           | AUX ACK, 4 bytes                             |

| 931        | 10247.81             | Source    | Native           | Req RD 16 bytes from 0x01400                 |

| 932        | 10247.90             | Sink      | Native           | AUX ACK, 16 bytes                            |

| 933        | 10247.90             | Sink T.   | Sb Reply         | DOWN_REP - REPLY: ALLOCATE_PAYLOAD           |

| 934        | 10247.90             | DPA-400   | ERROR            | AUX Transaction start error                  |

| 935        | 10247.94             | Unknown   | Event            | Changed:HPD=High                             |

| 936        | 10248.10             | Source    | Native           | Req RD 6 bytes from 0x00200                  |

| 937        | 10248.16             | Sink      | Native           | AUX ACK, 6 bytes                             |

| 938        | 10248.42             | Source    | Native           | Req WR 1 bytes to 0x02003                    |

| 939        | 10248.51             | Sink      | Native           | AUX ACK, O bytes                             |

| 940        | 10250.53             | Source    | Native           | Req RD 4 bytes from 0x02002                  |

| 941        | 10250.59             | Sink      | Native           | AUX ACK, 4 bytes                             |

|            |                      |           |                  | <del>_</del> :                               |

| 942        | 10250.85             | Source    | Native           | Req RD 1 bytes from Ux68U29                  |

| 942<br>943 | 10250.85<br>10250.91 |           | Native<br>Native | Req RD 1 bytes from 0x68029 AUX ACK, 1 bytes |

|            |                      | Sink      | Native           | AUX_ACK, 1 bytes                             |

#### Content decoder

Line #933 - 10247.90ms DOWN REP - REPLY: ALLOCATE PAYLOAD

-- Sideband message header -Link\_Count\_Total = 1

Link\_Count\_Remaining = 0

Broadcast\_Message = 0

Path\_Message = 1

MSG\_Body\_Length = 6

Start\_Of\_MT = 1

End\_Of\_MT = 1

Message Sequence No = 0

-- Sideband message validity check --MSG\_Header\_CRC = 5 [Good] MSG\_Body\_CRC = 7 [Good] Header Reserved (Zero) fields = Good

-- Message Transaction decoded -ACK

Request\_Identifier = 0x11 [ALLOCATE\_PAYLOAD]

Port\_Number = 8

Virtual\_Channel\_Payload\_ID = 2

Payload\_Bandwitdh\_Number = 689

Graphics driver may allocate all remaining bandwidth to the last device in the chain

#### Check GUID

|       |          | ~         |          | non non; , syoco                     |

|-------|----------|-----------|----------|--------------------------------------|

| 1037  | 56493.89 | Sink T.   | Sb Req.  | UP REQ - REQ: CONNECTION STATUS NOTI |

| 1038  | 56494.05 | Source    | Native   | Req WR 1 bytes to 0x02003            |

| 1039  | 56494.11 | Sink      | Native   | AUX ACK, O bytes                     |

| 1040  | 56494.24 | Source    | Native   | Req WR 5 bytes to 0x01200            |

| 1041  | 56494.24 | Source T. | Sb Reply | UP_REP - REPLY: CONNECTION_STATUS_NO |

| 1042  | 56494.37 | Sink      | Native   | AUX_ACK, O bytes                     |

| 1043  | 56494.50 | Source    | Native   | Req WR 12 bytes to 0x01000           |

| 1044  | 56494.50 | Source T. | Sb Req.  | DOWN_REQ - REQ: REMOTE_I2C_READ      |

| 1045  | 56494.94 | Sink      | Native   | AUX_DEFER, O bytes                   |

| 1046  | 56495.42 | Source    | Native   | Req WR 12 bytes to 0x01000           |

| 1047  | 56495.42 | Source T. | Sb Req.  | DOWN_REQ - REQ: REMOTE_I2C_READ      |

| 1048  | 56495.58 | Sink      | Native   | AUX_ACK, O bytes                     |

| 1049  | 56592.67 | Unknown   | Event    | Changed: HPD=Low                     |

| 1050  | 56593.60 | Unknown   | Event    | Changed:HPD=High                     |

| 1051  | 56593.63 | Source    | Native   | Req RD 6 bytes from 0x00200          |

| 1052  | 56593.73 | Sink      | Native   | AUX_ACK, 6 bytes                     |

| 1053  | 56594.05 | Source    | Native   | Req RD 4 bytes from 0x02002          |

| 1054  | 56594.11 | Sink      | Native   | AUX_ACK, 4 bytes                     |

| 1055  | 56594.24 | Source    | Native   | Req RD 16 bytes from 0x01400         |

| 1056  | 56594.34 | Sink      | Native   | AUX_ACK, 16 bytes                    |

| 1057  | 56594.56 | Source    | Native   | Req RD 16 bytes from 0x01410         |

| 1058  | 56594.66 | Sink      | Native   | AUX_ACK, 16 bytes                    |

| 1059  | 56594.88 | Source    | Native   | Req RD 7 bytes from 0x01420          |

| 1060  | 56594.98 | Sink      | Native   | AUX_ACK, 7 bytes                     |

| 1061  | 56594.98 | Sink T.   | Sb Reply | DOWN_REP - Message Transaction fragm |

|       | 56595.14 | Source    | Native   | Req WR 1 bytes to 0x02003            |

| 1063  | 56595.20 | Sink      | Native   | AUX_ACK, O bytes                     |

|       | E66E1 E0 | Unirnorm  | Frron+   | Changed PDD-Low                      |

| 11064 |          |           |          |                                      |

#### Content decoder

Line #1037 - 56493.89ms UP\_REQ - REQ: CONNECTION\_STATUS\_NOTIFY

-- Sideband message header -Link\_Count\_Total = 1

Link\_Count\_Remaining = 7

Broadcast\_Message = 1

Path\_Message = 0

MSG\_Body\_Length = 20

Start\_Of\_MT = 1

End\_Of\_MT = 1

Message\_Sequence\_No = 0

-- Sideband message validity check --MSG\_Header\_CRC = 6 [Good] MSG\_Body\_CRC = 193 [Good] Header Reserved (Zero) fields = Good

-- Message Transaction decoded -CONNECTION\_STATUS\_NOTIFY (0x02):

Port\_Number = 1

Global\_Unique\_Identifier = 0x10de9070000000217ed235500000096

Legacy\_Device\_Plug\_Status = 0

DisplayPort\_Device\_Plug\_Status = 1

Messaging\_Capability\_Status = 0

Input\_Port = 0

Peer\_Device\_Type = 3

## Interoperability Test

### Test Equipment for Demo

**Aux Monitor**

**Branch Sink**

**Branch Sink**

### Test Configuration A for Demo

Let's GO

### Test Configuration B for Demo

DPA-400

**Aux Monitor**

**Branch Sink**

**Branch Sink**

## Let's GO

## One Stop Logo Solution at Allion

#### **Bus Interface**

#### Radio Frequency

#### OS, Content & Storages

# Thank you!

2012 © ALLION LABS, INC. ALL RIGHTS RESERVED. NO TEXT, LOGO OR GRAPHIC FROM THIS DOCUMENT MAY BE COPIED OR RETRANSMITTED UNLESS EXPRESSLY PERMITTED BY ALLION TEST LABS, INC. AND THEIR RESPECTIVE OWNERS.